Part Datasheet Search > Digital Signal Processors(DSPs) > TMS320C6748 Datasheet PDF

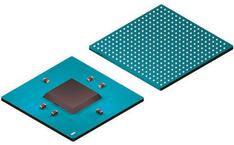

Images are for reference

TMS320C6748 Datasheet PDF

Part Series:

TMS320C6748 Series

Category:

Digital Signal Processors(DSPs)

Description:

DSP Fixed-Point/Floating-Point 64Bit 456MHz 3648MIPS 361Pin NFBGA

Updated Time: 2023/01/13 02:03:29 (UTC + 8)

TMS320C6748 Digital Signal Processors(DSPs) Datasheet PDF

TMS320C6748 Datasheet PDF Digital Signal Processors(DSPs)

275 Pages

TI

DSP Fixed-Point/Floating-Point 64Bit 456MHz 3648MIPS 361Pin NFBGA

275 Pages

TI

DSP Fixed-Point/Floating-Point 64Bit 375MHz 3000MIPS 361Pin NFBGA

275 Pages

TI

DSP Fixed-Point/Floating-Point 64Bit 456MHz 3648MIPS 361Pin NFBGA

275 Pages

TI

DSP Fixed-Point/Floating-Point 64Bit 375MHz 3000MIPS 361Pin NFBGA

275 Pages

TI

DSP Fixed-Point/Floating-Point 64Bit 456MHz 3648MIPS 361Pin NFBGA

275 Pages

TI

DSP Fixed-Point/Floating-Point 64Bit 375MHz 3000MIPS 361Pin NFBGA

Part Datasheet PDF Search

72,405,303 Parts Datasheet PDF, Update more than 5,000 PDF files ervery day.